随着集成电路器件尺寸的不断微缩,全包围环形栅(Gate-all-around)器件成为先进工艺节点的重要技术,然而GAA器件工艺复杂,技术挑战巨大。

As the size of IC devices continues to shrink, gate-all-around devices have become an important technology for advanced process nodes. However, the technical challenges are still huge in terms of the process fabrication.

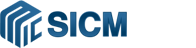

上海集成电路材料研究院研发具有内嵌空腔的SOI衬底(Void Embedded Silicon on Insulator,即VESOI)(图1),并成功应用于GAA器件的制备。

The Shanghai Institute of IC Materials (SICM) and the Shanghai Institute of Microsystem and Information Technology Chinese, Academy of Sciences (SIMIT, CAS) developed an SOI substrate (Void Embedded Silicon-on-Insulator, VESOI) with embedded cavities (Figure 1), and successfully applied it in the fabrication of GAA devices.

图1 SOI与VESOI衬底对比 Figure 1 SOI substrate vs. VESOI

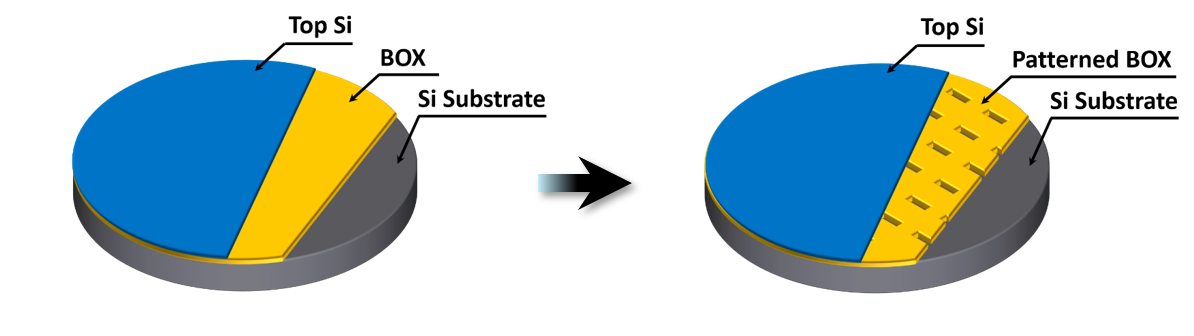

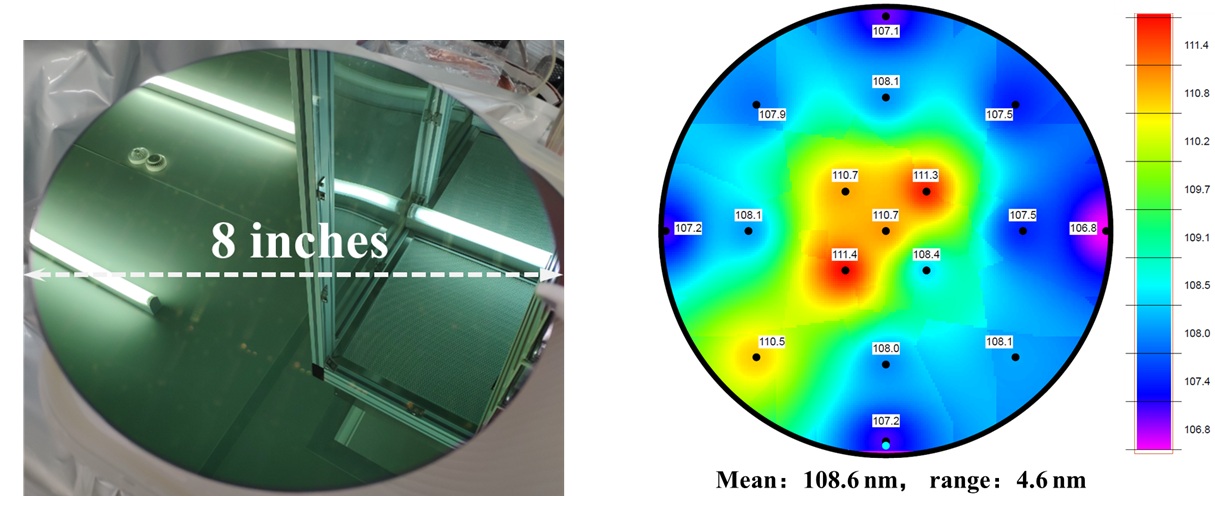

研发团队制备出8英寸VESOI衬底(图2),实现了空腔结构在SOI衬底中的高密度排列。在8英寸VESOI衬底上,利用与普通平面CMOS工艺完全兼容的工艺流程,制备出GAA器件(图3)。

The research team developed an 8-inch VESOI substrate (Figure 2), which achieved the high-density arrangement of the cavity structure in the SOI substrate. GAA devices are fabricated on an 8-inch VESOI substrate using a process flow that is fully compatible with common planar CMOS processes (Figure 3).

图2 8英寸VESOI衬底实物图 Figure 2 8-inch VESOI substrate

图3 GAA器件流程简要示意图 Figure 3 Schematic diagram of GAA device process flow

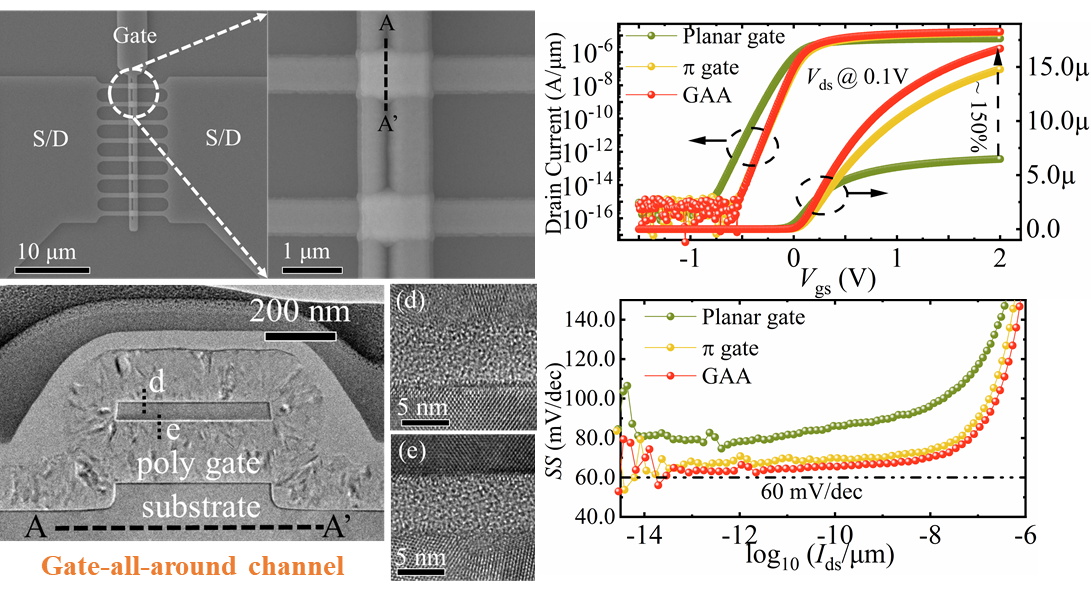

VESOI GAA器件的栅极完全包裹了导电沟道,沟道上方和下方的栅氧层厚度一致,并表现出了优异的电学性能(图4),其最小亚阈值斜率小于63mV/dec,电流密度较平面SOI器件最高可提升150%以上。

The gate of the VESOI GAA device completely wraps the conductive channel with the same gate oxide thickness above and below the channel. And the device shows excellent electrical performance (Figure 4). Its minimum subthreshold slope is less than 63mV/dec, and the current density can be increased by more than 150% compared with planar SOI devices.

图4 基于VESOI衬底的GAA器件表现出优良电学性能 Figure 4 Excellent electrical performance on GAA devices based on VESOI substrate

与目前常用的GAA器件工艺相比,VESOI GAA器件工艺大大简化,并可兼容大部分工艺节点。VESOI GAA既可用于先进工艺节点器件,也可对成熟工艺节点进行性能升级。研发团队同时还在开发将VESOI应用于传感器、射频器件等一系列技术,以期满足更广泛的应用需求。

Compared with the commonly-used GAA device process recently, the VESOI GAA device fabrication is significantly simplified and compatible with most planar process nodes. It can be used not only in processes beyond advanced nodes, but also for upgrading performance on mature ones.The research team is developing a series of technologies that apply VESOI to sensors, RF devices, etc., to meet a wider range of application requirements.

上海集成电路材料研究院 Shanghai Institute of IC Materials

上海集成电路材料研究院聚焦集成电路衬底材料、工艺材料和前沿技术的研发与产业化。

The Shanghai Institute of IC Materials was initiated and established by the SIMIT, CAS and National Silicon Industry Group, focusing on the R&D and industrialization of integrated circuit substrate materials, fabrication materials and cutting-edge technologies.

联系我们Contact Us: info@sicm.com.cn